# STELLA MARIS COLLEGE (AUTONOMOUS) CHENNAI – 600 086.

(For candidates admitted during the academic year 2008-09 & thereafter)

SUBJECT CODE: PH/MC/EL14

REG. No.\_\_\_\_\_

## B.Sc. DEGREE EXAMINATION NOVEMBER 2010 **BRANCH III - PHYSICS**

Ι

FIRST SEMESTER

| COURSE        |                                        | MAJOR – CORE                                             |                                                                                         |                                      |  |  |

|---------------|----------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------|--|--|

| PAPER<br>TIME |                                        | LECTRONICS I<br>0 MINS.                                  |                                                                                         | MAX. MARKS : 30                      |  |  |

| IIIVIL        | . 3                                    |                                                          | ON – A                                                                                  | IVIAA. IVIANNO . 30                  |  |  |

|               | TO BI                                  | E ANSWERED IN THE                                        |                                                                                         | ITSELF                               |  |  |

| A             | NSWER ALL                              | QUESTIONS:                                               |                                                                                         | $(30 \times 1 = 30)$                 |  |  |

| I CHO         | OSE THE CO                             | ORRECT ANSWERS:                                          |                                                                                         |                                      |  |  |

| (a)           | zero                                   | theorem, the output<br>on load resistance                | voltage of an ideal voltage source is (b) constant (d) dependent on internal resistance |                                      |  |  |

| (0)           | асрепаен (                             | on load resistance                                       | (a) dependent o                                                                         | (d) dependent on internal resistance |  |  |

| del           |                                        | dition of maximum p<br>wer of 30 W to the lo<br>(b) 45 W |                                                                                         | _                                    |  |  |

| 3.            | A ———————————————————————————————————— | — The output of                                          | this gate is                                                                            |                                      |  |  |

| (             | a) A.B                                 | (b) <i>A</i> .B                                          | (c) $\overline{A+B}$                                                                    | (d) A+B                              |  |  |

|               | $\bar{A} + B$ ) = ? $\bar{A}.B$        | (b) A. $\bar{B}$                                         | (c) A + B                                                                               | (d) A.B                              |  |  |

| 5 Th          | e fundamen                             | tal product is also te                                   | rmed as                                                                                 |                                      |  |  |

|               |                                        | (b) Maxterm                                              | (c) POS                                                                                 | (d) SOP                              |  |  |

|               |                                        | which all inputs mus<br>b) an AND gate (c)               |                                                                                         |                                      |  |  |

|               | NOT gate is a<br>an inverter           | also called as<br>(b) a converter                        | (c) a rectifier                                                                         | (d) an universal gate                |  |  |

|               | e four 1's gr<br>) a Pair              | ouped together in a l<br>(b) a Quad                      | 0 1                                                                                     | alled<br>(d) a group                 |  |  |

|               | a                                      |                                                          |                                                                                         |                                      |  |  |

|               | mbination ci<br>a) NAND-NA             | rcuit<br>ND (b) NOR-NOR                                  | (c) NOR-NAND                                                                            | (d) OR-AND                           |  |  |

|               |                                        |                                                          |                                                                                         | 2                                    |  |  |

..3..

|                                                                       | 10.                                                                                                                                |                                                          | ving flip flops is us<br>(b) D flip flop |                                                                         | (d) T flip flop      |  |  |  |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------|----------------------|--|--|--|

|                                                                       | <ul><li>11. A ring counter is same as</li><li>(a) Up-Down counter</li><li>(c) Shift register</li></ul>                             |                                                          |                                          | <ul><li>(b) Parallel counter</li><li>(d) Asynchronous counter</li></ul> |                      |  |  |  |

|                                                                       | 12.                                                                                                                                | This cannot be fab<br>(a) diodes                         | ricated on an IC<br>(b) transistors      | (c) resistors                                                           | (d) transformers     |  |  |  |

| -                                                                     | 13.                                                                                                                                | The number of cor<br>(a) 20 to 100<br>(c) 1000 to 10,000 | -                                        | (b) 100 to 1000<br>(d) 10,000 to 1,00                                   | 0,000                |  |  |  |

|                                                                       | 14.                                                                                                                                | The $SiO_2$ layer in a (a) a resistor (c) a capacitor    | nn IC acts as                            | (b) an insulating l<br>(d) mechanical ou                                | ž.                   |  |  |  |

|                                                                       |                                                                                                                                    | Most popular type<br>(a) thin film (b) th                |                                          | brid (d) m                                                              | onolithic            |  |  |  |

| II                                                                    | S                                                                                                                                  | TATE WHETHER T                                           | RUE OR FALSE                             |                                                                         |                      |  |  |  |

|                                                                       | 16                                                                                                                                 | A                                                        | is a NOR gate.                           |                                                                         |                      |  |  |  |

|                                                                       | 17. $AB\bar{C} + \bar{A}\bar{B}C$ is a SOP expression.<br>18. In a Karnaugh map, 'Don't Care' conditions are represented as 'Zeros |                                                          |                                          |                                                                         |                      |  |  |  |

|                                                                       |                                                                                                                                    |                                                          |                                          |                                                                         |                      |  |  |  |

|                                                                       | 19                                                                                                                                 | . The expression fo                                      | or 'borrow' in a full                    | subtractor is $\bar{A}$ B                                               | + BC + C $\bar{A}$ . |  |  |  |

|                                                                       | 20. Shift registers can be constructed using JK flip flops.                                                                        |                                                          |                                          |                                                                         |                      |  |  |  |

| III                                                                   | F                                                                                                                                  | ILL IN THE BLANK                                         | XS:                                      |                                                                         |                      |  |  |  |

|                                                                       | 21. Norton's theorem is of Thevenis's theorem.                                                                                     |                                                          |                                          |                                                                         |                      |  |  |  |

|                                                                       | resistance (R <sub>i</sub> ), the                                                                                                  |                                                          |                                          |                                                                         |                      |  |  |  |

|                                                                       | 23                                                                                                                                 | 3. The Norton's current is sometimes called as current.  |                                          |                                                                         |                      |  |  |  |

|                                                                       | 24                                                                                                                                 | . Using Duality pr                                       | 1 becomes                                |                                                                         |                      |  |  |  |

| 25. When clock is applied simultaneously to all flip flops, it is cal |                                                                                                                                    |                                                          |                                          |                                                                         |                      |  |  |  |

## IV ANSWER IN ONE OR TWO SENTENCES:

| $\sim$ | <b>Q</b> | 771    | ٠,    | 771   |        |

|--------|----------|--------|-------|-------|--------|

| ソわ     | State    | Thev   | ഘവന ( | a The | $^{2}$ |

| 20.    | Diale    | 1110 0 |       |       |        |

27. How is resistance  $R_N$  measured in Norton's network

28. Find the compliment of  $A + \overline{B + \overline{CD}}$

29. What is meant by modulus of a counter? How many states are there in a mod 8 counter?

30. What is meant by a monolithic IC?

## STELLA MARIS COLLEGE (AUTONOMOUS), CHENNAI - 600 086

(For candidates admitted during the academic year 2008 – 09 & thereafter)

SUBJECT CODE: PH/MC/EL14

#### **B.Sc. DEGREE EXAMINATION NOVEMBER 2010**

BRANCH III – PHYSICS First Semester

COURSE: MAJOR - CORE PAPER: ELECTRONICS I

TIME: 2½ HOURS MAX. MARKS: 70

#### SECTION - B

### ANSWER ANY **FIVE** QUESTIONS:

$(5 \times 5 = 25)$

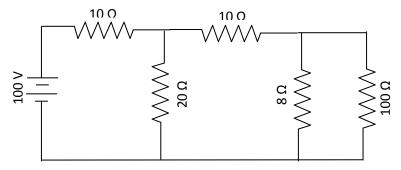

1. Using Thevenin's Theorem, find the current through 100  $\Omega$  resistance connected across terminals A & B in the following circuit.

- 2. State and prove De Morgan's Theorem.

- 3. State the laws of Boolean algebra and classify them.

- 4. Explain a D flip flop and its functioning.

- 5. Simplify using Karnaugh map:  $Y = f(A, B, C,D) = \sum (0,2,5,7,8,10,13,15)$ .

- 6. Explain the working of a Ripple counter.

- 7. State some advantages and disadvantages of Integrated Circuits.

#### **SECTION - C**

### ANSWER ANY **THREE** QUESTIONS:

$(3 \times 15 = 45)$

- 8. Explain Norton's theorem with an example.

- 9. Explain the working of an half adder and a full adder with neat diagrams

- 10. Show that NOR and NAND gates are Universal building blocks.

- 11. Explain with circuit, the working of (i) an RS flip flop and (ii) a JK Master-slave flip flop.

- 12. Describe the fabrication of a Monolithic IC.

### \$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$